FPGA Project in CS@Fudan

Updated:

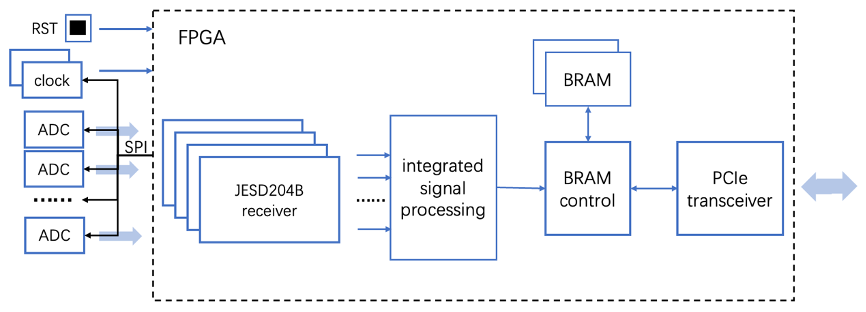

A PCIe data acquisition board is designed to verify the hardware and algorithm of 8 ADC time interleaved sampling based on Virtex-7 FPGA.

Updated:

A PCIe data acquisition board is designed to verify the hardware and algorithm of 8 ADC time interleaved sampling based on Virtex-7 FPGA.

Updated:

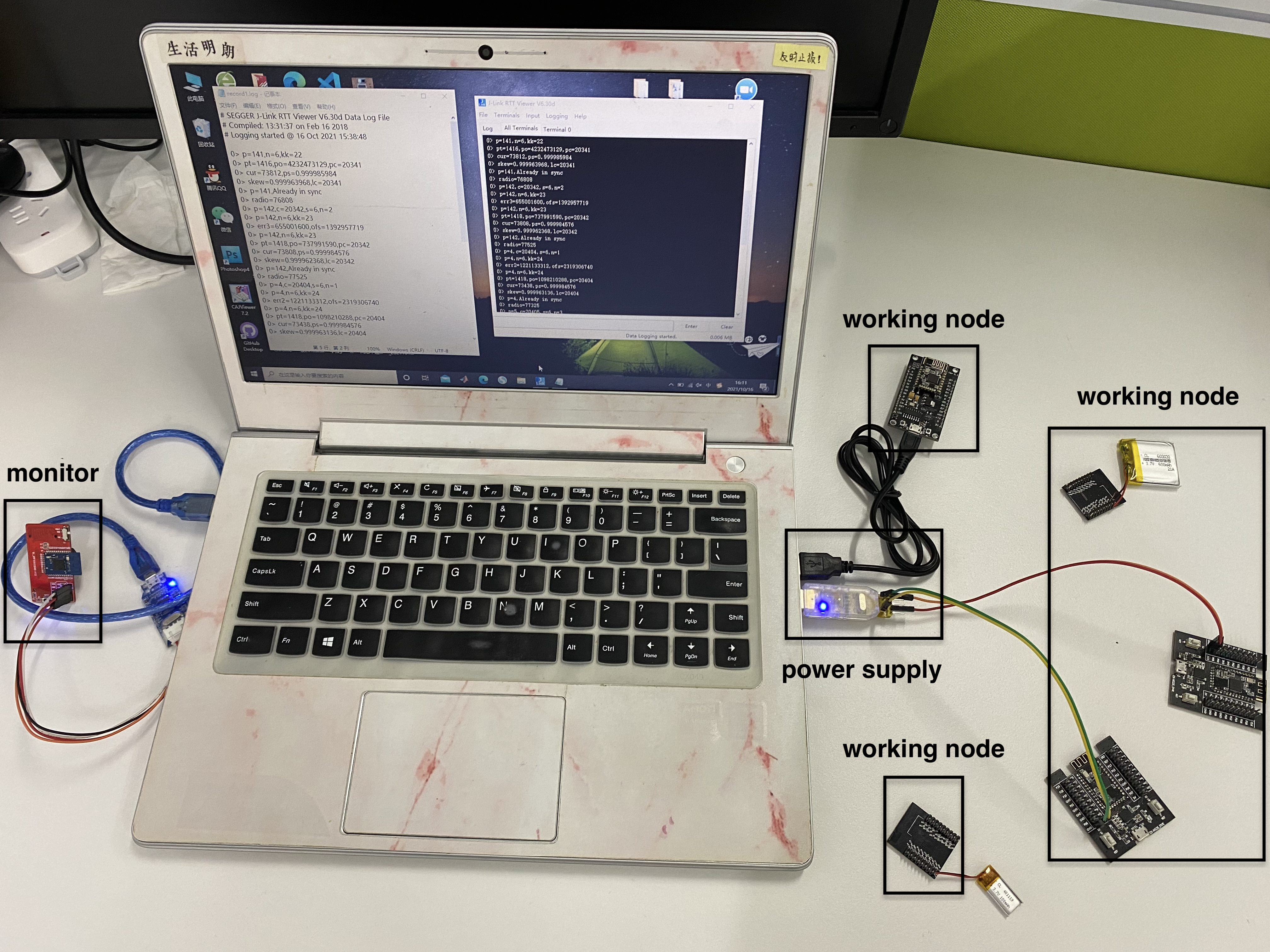

We propose a joint design of delay compensation and one-way synchronization, which achieves estimation of clock parameters and fluctuated message delays at the same time.

Updated:

We integrated various protocol interface outside and form an unified authentication platform.

Updated:

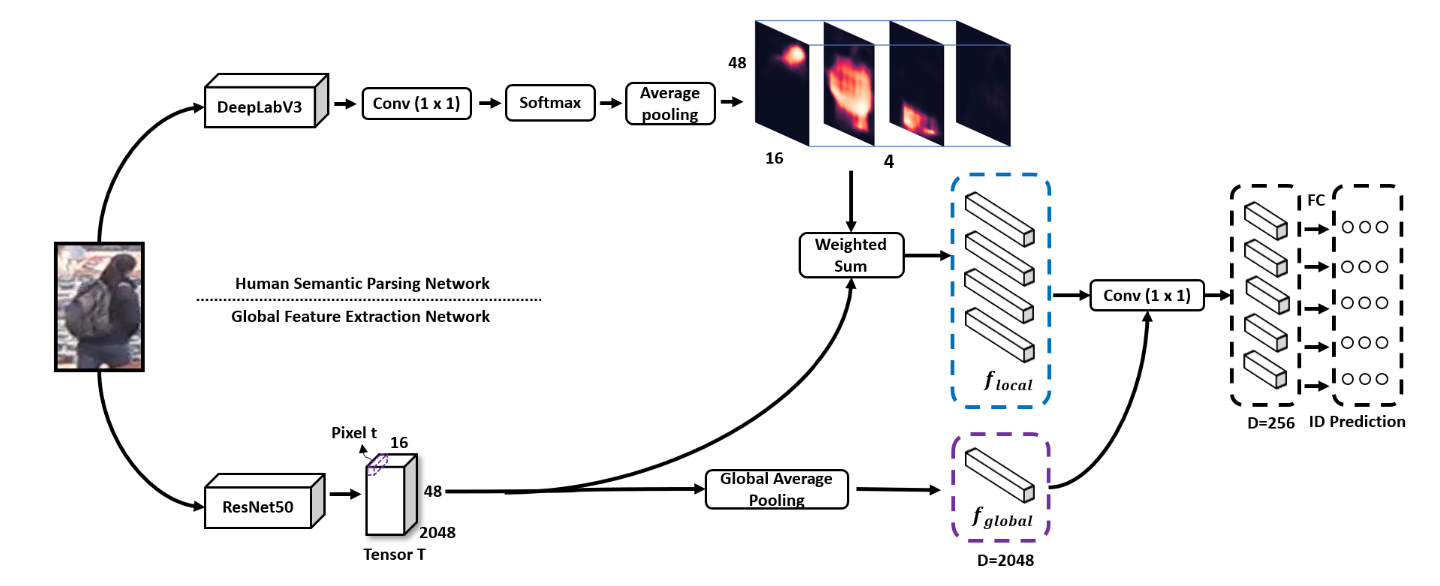

We propose a semantic-guided alignment model that uses image semantic information to separate useful information from occlusion noise.